# Z80°-CPU Z80A°-CPU

Technical Manual

Price: \$7.50 03-0029-01

Copyright© 1977 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog.

Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

### **Reader's Comments**

Your feedback about this document helps us ascertain your needs and fulfill them in the future. Please take the time to fill out this questionaire and return it to us. This information will be helpful to us and, in time, to future users of Zilog products.

| Your Name:                                                                              |

|-----------------------------------------------------------------------------------------|

| Company Name:                                                                           |

| Address:                                                                                |

| Title of this document:                                                                 |

| Briefly describe application:                                                           |

|                                                                                         |

|                                                                                         |

|                                                                                         |

| Does this publication meet your needs?   Yes  No If not, why not?                       |

|                                                                                         |

| · · · · · · · · · · · · · · · · · · ·                                                   |

| How are you using this publication?                                                     |

| How are you using this publication?                                                     |

| ☐ As an introduction to the subject?                                                    |

| ☐ As a reference manual?                                                                |

| ☐ As an instructor or student?                                                          |

| How do you find the material?                                                           |

| Excellent Good Poor                                                                     |

| Technicality $\square$ $\square$                                                        |

| Organization $\square$ $\square$                                                        |

| Completeness $\square$ $\square$ $\square$                                              |

|                                                                                         |

| What would have improved the material?                                                  |

|                                                                                         |

|                                                                                         |

|                                                                                         |

| Other comments and suggestions:                                                         |

|                                                                                         |

|                                                                                         |

|                                                                                         |

| If you found any mistakes in this document, please let us know what and where they are: |

|                                                                                         |

|                                                                                         |

NO POSTAGE

NECESSARY

IF MAILED

IN THE

UNITED STATES

### **BUSINESS REPLY MAIL**

FIRST CLASS PERMIT NO. 475 CUPERTINO, CA

POSTAGE WILL BE PAID BY

### Zilog

Publications Department Semiconductor Division 10341 Bubb Road Cupertino, California 95014

### TABLE OF CONTENTS

| Chapter |                                         | Pa | ige |

|---------|-----------------------------------------|----|-----|

| 1.0     | Introduction                            |    | 1   |

| 2.0     | Z80-CPU Architecture                    |    | 3   |

| 3.0     | Z80-CPU Pin Description                 |    | 7   |

| 4.0     | CPU Timing                              | •  | 11  |

| 5.0     | Z80-CPU Instruction Set                 |    | 19  |

| 6.0     | Flags                                   |    | 39  |

| 7.0     | Summary of OP Codes and Execution Times | •  | 43  |

| 8.0     | Interrupt Response                      |    | 55  |

| 9.0     | Hardware Implementation Examples        |    | 59  |

| 10.0    | Software Implementation Examples        | •  | 63  |

| 11.0    | Electrical Specifications               | •  | 69  |

| 12.0    | 700 CDI In standation Set Summany       |    | 72  |

#### 1.0 INTRODUCTION

The term "microcomputer" has been used to describe virtually every type of small computing device designed within the last few years. This term has been applied to everything from simple "microprogrammed" controllers constructed out of TTL MSI up to low end minicomputers with a portion of the CPU constructed out of TTL LSI "bit slices." However, the major impact of the LSI technology within the last few years has been with MOS LSI. With this technology, it is possible to fabricate complete and very powerful computer systems with only a few MOS LSI components.

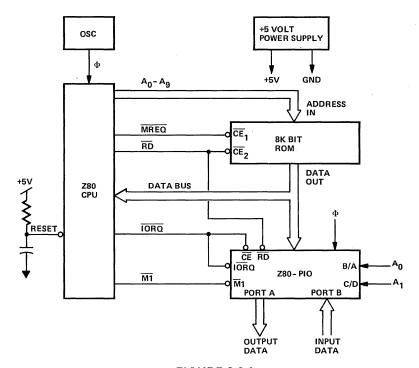

The Zilog Z-80 family of components is a significant advancement in the state-of-the art of micro-computers. These components can be configured with any type of standard semiconductor memory to generate computer systems with an extremely wide range of capabilities. For example, as few as two LSI circuits and three standard TTL MSI packages can be combined to form a simple controller. With additional memory and I/O devices a computer can be constructed with capabilities that only a minicomputer could previously deliver. This wide range of computational power allows standard modules to be constructed by a user that can satisfy the requirements of an extremely wide range of applications.

The major reason for MOS LSI domination of the microcomputer market is the low cost of these few LSI components. For example, MOS LSI microcomputers have already replaced TTL logic in such applications as terminal controllers, peripheral device controllers, traffic signal controllers, point of sale terminals, intelligent terminals and test systems. In fact the MOS LSI microcomputer is finding its way into almost every product that now uses electronics and it is even replacing many mechanical systems such as weight scales and automobile controls.

The MOS LSI microcomputer market is already well established and new products using them are being developed at an extraordinary rate. The Zilog Z-80 component set has been designed to fit into this market through the following factors:

- 1. The Z-80 is fully software compatible with the popular 8080A CPU offered from several sources. Existing designs can be easily converted to include the Z-80 as a superior alternative.

- 2. The Z-80 component set is superior in both software and hardware capabilities to any other micro-computer system on the market. These capabilities provide the user with significantly lower hardware and software development costs while also allowing him to offer additional features in his system.

- 3. For increased throughput the Z80A operating at a 4 MHZ clock rate offers the user significant speed advantages over competitive products.

- 4. A complete product line including full software support with strong emphasis on high level languages and a disk-based development system with advanced real-time debug capabilities is offered to enable the user to easily develop new products.

Microcomputer systems are extremely simple to construct using Z-80 components. Any such system consists of three parts:

- 1. CPU (Central Processing Unit)

- 2. Memory

- 3. Interface Circuits to peripheral devices

The CPU is the heart of the system. Its function is to obtain instructions from the memory and perform the desired operations. The memory is used to contain instructions and in most cases data that is to be processed. For example, a typical instruction sequence may be to read data from a specific peripheral device, store it in a location in memory, check the parity and write it out to another peripheral device. Note that the Zilog component set includes the CPU and various general purpose I/O device controllers, while a wide range of memory devices may be used from any source. Thus, all required components can be connected together in a very simple manner with virtually no other external logic. The user's effort then becomes primarily one of software development. That is, the user can concentrate on describing his problem and translating it into a series of instructions that can be loaded into the microcomputer memory. Zilog is dedicated to making this step of software generation as simple as possible. A good example of this is our

assembly language in which a simple mnemonic is used to represent every instruction that the CPU can perform. This language is self documenting in such a way that from the mnemonic the user can understand exactly what the instruction is doing without constantly checking back to a complex cross listing.

#### 2.0 Z-80 CPU ARCHITECTURE

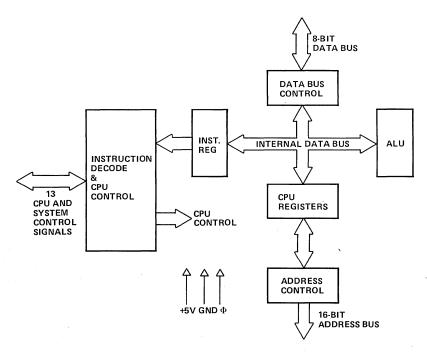

A block diagram of the internal architecture of the Z-80 CPU is shown in figure 2.0-1. The diagram shows all of the major elements in the CPU and it should be referred to throughout the following description.

Z-80 CPU BLOCK DIAGRAM FIGURE 2,0-1

#### 2.1 CPU REGISTERS

The Z-80 CPU contains 208 bits of R/W memory that are accessible to the programmer. Figure 2.0-2 illustrates how this memory is configured into eighteen 8-bit registers and four 16-bit registers. All Z-80 registers are implemented using static RAM. The registers include two sets of six general purpose registers that may be used individually as 8-bit registers or in pairs as 16-bit registers. There are also two sets of accumulator and flag registers.

#### **Special Purpose Registers**

- 1. **Program Counter (PC).** The program counter holds the 16-bit address of the current instruction being fetched from memory. The PC is automatically incremented after its contents have been transferred to the address lines. When a program jump occurs the new value is automatically placed in the PC, overriding the incrementer.

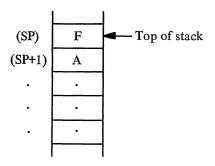

- 2. Stack Pointer (SP). The stack pointer holds the 16-bit address of the current top of a stack located anywhere in external system RAM memory. The external stack memory is organized as a last-in first-out (LIFO) file. Data can be pushed onto the stack from specific CPU registers or popped off of the stack into specific CPU registers through the execution of PUSH and POP instructions. The data popped from the stack is always the last data pushed onto it. The stack allows simple implementation of multiple level interrupts, unlimited subroutine nesting and simplification of many types of data manipulation.

| MAIN F           | EG SET     | ALTERNAT          | TE REG SET  |                                 |

|------------------|------------|-------------------|-------------|---------------------------------|

| ACCUMULATOR<br>A | FLAGS<br>F | ACCUMULATOR<br>A' | FLAGS<br>F' |                                 |

| В                | С          | B'                | C'          |                                 |

| D                | E          | D'                | E'          | GENERAL<br>PURPOSE<br>REGISTERS |

| H L              |            | H'                | L'          |                                 |

| INTERRUPT<br>VECTOR<br>I | MEMORY<br>REFRESH<br>R |                   |

|--------------------------|------------------------|-------------------|

| INDEX REGISTE            | SPECIAL                |                   |

| INDEX REGISTE            | RIY                    | PURPOSE REGISTERS |

| STACK POINTER            |                        |                   |

| PROGRAM COU              | ]]                     |                   |

#### Z-80 CPU REGISTER CONFIGURATION FIGURE 2.0-2

- 3. Two Index Registers (IX & IY). The two independent index registers hold a 16-bit base address that is used in indexed addressing modes. In this mode, an index register is used as a base to point to a region in memory from which data is to be stored or retrieved. An additional byte is included in indexed instructions to specify a displacement from this base. This displacement is specified as a two's complement signed integer. This mode of addressing greatly simplifies many types of programs, especially where tables of data are used.

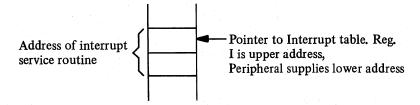

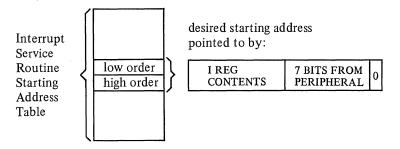

- 4. Interrupt Page Address Register (I). The Z-80 CPU can be operated in a mode where an indirect call to any memory location can be achieved in response to an interrupt. The I Register is used for this purpose to store the high order 8-bits of the indirect address while the interrupting device provides the lower 8-bits of the address. This feature allows interrupt routines to be dynamically located anywhere in memory with absolute minimal access time to the routine.

- 5. Memory Refresh Register (R). The Z-80 CPU contains a memory refresh counter to enable dynamic memories to be used with the same ease as static memories. Seven bits of this 8 bit register are automatically incremented after each instruction fetch. The eighth bit will remain as programmed as the result of an LD R, A instruction. The data in the refresh counter is sent out on the lower portion of the address bus along with a refresh control signal while the CPU is decoding and executing the fetched instruction. This mode of refresh is totally transparent to the programmer and does not slow down the CPU operation. The programmer can load the R register for testing purposes, but this register is normally not used by the programmer. During refresh, the contents of the I register are placed on the upper 8 bits of the address bus.

#### Accumulator and Flag Registers

The CPU includes two independent 8-bit accumulators and associated 8-bit flag registers. The accumulator holds the results of 8-bit arithmetic or logical operations while the flag register indicates specific conditions for 8 or 16-bit operations, such as indicating whether or not the result of an operation is equal to zero. The programmer selects the accumulator and flag pair that he wishes to work with with a single exchange instruction so that he may easily work with either pair.

#### **General Purpose Registers**

There are two matched sets of general purpose registers, each set containing six 8-bit registers that may be used individually as 8-bit registers or as 16-bit register pairs by the programmer. One set is called BC, DE and HL while the complementary set is called BC', DE' and HL'. At any one time the programmer can select either set of registers to work with through a single exchange command for the entire set. In systems where fast interrupt response is required, one set of general purpose registers and an accumulator/flag register may be reserved for handling this very fast routine. Only a simple exchange commands need be executed to go between the routines. This greatly reduces interrupt service time by eliminating the requirement for saving and retrieving register contents in the external stack during interrupt or subroutine processing. These general purpose registers are used for a wide range of applications by the programmer. They also simplify programming, especially in ROM based systems where little external read/write memory is available.

#### 2.2 ARITHMETIC & LOGIC UNIT (ALU)

The 8-bit arithmetic and logical instructions of the CPU are executed in the ALU. Internally the ALU communicates with the registers and the external data bus on the internal data bus. The type of functions performed by the ALU include:

Add Left or right shifts or rotates (arithmetic and logical)

Subtract Increment

Logical AND Decrement

Logical OR Set bit

Logical Exclusive OR Reset bit

Compare Test bit

#### 2.3 INSTRUCTION REGISTER AND CPU CONTROL

As each instruction is fetched from memory, it is placed in the instruction register and decoded. The control sections performs this function and then generates and supplies all of the control signals necessary to read or write data from or to the registers, control the ALU and provide all required external control signals.

#### 3.0 Z-80 CPU PIN DESCRIPTION

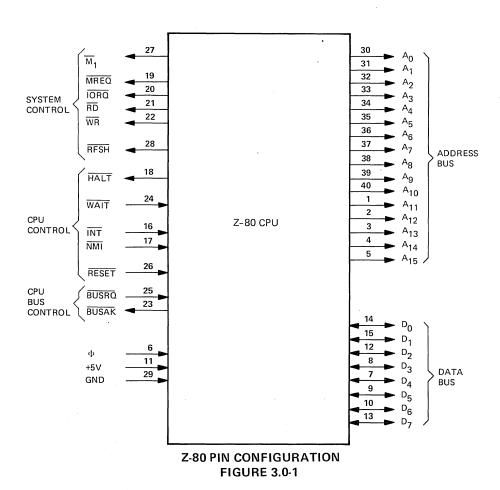

The Z-80 CPU is packaged in an industry standard 40 pin Dual In-Line Package. The I/O pins are shown in figure 3.0-1 and the function of each is described below.

A<sub>0</sub>-A<sub>15</sub> (Address Bus) Tri-state output, active high.  $A_0$ - $A_{15}$  constitute a 16-bit address bus. The address bus provides the address for memory (up to 64K bytes) data exchanges and for I/O device data exchanges. I/O addressing uses the 8 lower address bits to allow the user to directly select up to 256 input or 256 output ports.  $A_0$  is the least significant address bit. During refresh time, the lower 7 bits contain a valid refresh address.

D<sub>0</sub>-D<sub>7</sub> (Data Bus)

Tri-state input/output, active high.  $D_0$ - $D_7$  constitute an 8-bit bidirectional data bus. The data bus is used for data exchanges with memory and I/O devices.

M<sub>1</sub>

(Machine Cycle one)

Output, active low.  $\overline{M}_1$  indicates that the current machine cycle is the OP code fetch cycle of an instruction execution. Note that during execution of 2-byte op-codes,  $\overline{M}_1$  is generated as each op code byte is fetched. These two byte op-codes always begin with CBH, DDH, EDH or FDH.  $\overline{M}_1$  also occurs with  $\overline{10RQ}$  to indicate an interrupt acknowledge cycle.

MREQ (Memory Request)

Tri-state output, active low. The memory request signal indicates that the address bus holds a valid address for a memory read or memory write operation.

**IORO**

(Input/Output Request)

Tri-state output, active low. The  $\overline{IORQ}$  signal indicates that the lower half of the address bus holds a valid I/O address for a I/O read or write operation. An  $\overline{IORQ}$  signal is also generated with an  $\overline{M1}$  signal when an interrupt is being acknowledged to indicate that an interrupt response vector can be placed on the data bus. Interrupt Acknowledge operations occur during  $M_1$  time while I/O operations never occur during  $M_1$  time.

RD

(Memory Read)

Tri-state output, active low. RD indicates that the CPU wants to read data from memory or an I/O device. The addressed I/O device or memory should use this signal to gate data onto the CPU data bus.

WR

(Memory Write)

Tri-state output, active low. WR indicates that the CPU data bus holds valid data to be stored in the addressed memory or I/O device.

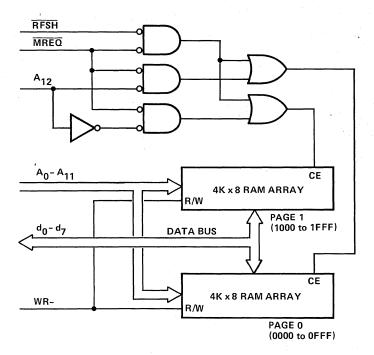

RFSH (Refresh)

Output, active low. RFSH indicates that the lower 7 bits of the address bus contain a refresh address for dynamic memories and the current MREQ signal should be used to do a refresh read to all dynamic memories.

HALT (Halt state)

Output, active low. HALT indicates that the CPU has executed a HALT software instruction and is awaiting either a non maskable or a maskable interrupt (with the mask enabled) before operation can resume. While halted, the CPU executes NOP's to maintain memory refresh activity.

WAIT (Wait)

Input, active low. WAIT indicates to the Z-80 CPU that the addressed memory or I/O devices are not ready for a data transfer. The CPU continues to enter wait states for as long as this signal is active. This signal allows memory or I/O devices of any speed to be synchronized to the CPU.

INT

(Interrupt Request)

Input, active low. The Interrupt Request signal is generated by I/O devices. A request will be honored at the end of the current instruction if the internal software controlled interrupt enable flip-flop (IFF) is enabled and if the  $\overline{\rm BUSRQ}$  signal is not active. When the CPU accepts the interrupt, an acknowledge signal ( $\overline{\rm IORQ}$  during M  $_1$  time) is sent out at the beginning of the next instruction cycle. The CPU can respond to an interrupt in three different modes that are described in detail in section 5.4 (CPU Control Instructions).

NMI (Non Maskable Interrupt)

Input, negative edge triggered. The non maskable interrupt request line has a higher priority than  $\overline{INT}$  and is always recognized at the end of the current instruction, independent of the status of the interrupt enable flip-flop.  $\overline{NMI}$  automatically forces the Z-80 CPU to restart to location  $0066_H$ . The program counter is automatically saved in the external stack so that the user can return to the program that was interrupted. Note that continuous WAIT cycles can prevent the current instruction from ending, and that a  $\overline{BUSRQ}$  will override a  $\overline{NMI}$ .

#### RESET

Input, active low. RESET forces the program counter to zero and initializes the CPU. The CPU initialization includes:

- 1) Disable the interrupt enable flip-flop

- 2) Set Register  $I = 00_{H}$

- 3) Set Register  $R = 00_{H}$

- 4) Set Interrupt Mode 0

During reset time, the address bus and data bus go to a high impedance state and all control output signals go to the inactive state.

### BUSRQ (Bus Request)

Input, active low. The bus request signal is used to request the CPU address bus, data bus and tri-state output control signals to go to a high impedance state so that other devices can control these buses. When  $\overline{BUSRQ}$  is activated, the CPU will set these buses to a high impedance state as soon as the current CPU machine cycle is terminated.

# BUSAK (Bus Acknowledge)

Output, active low. Bus acknowledge is used to indicate to the requesting device that the CPU address bus, data bus and tri-state control bus signals have been set to their high impedance state and the external device can now control these signals.

Φ

Single phase TTL level clock which requires only a 330 ohm pull-up resistor to +5 volts to meet all clock requirements.

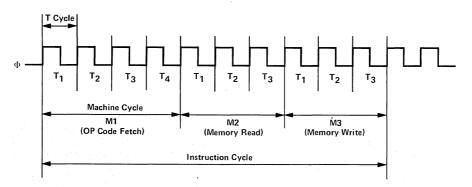

#### 4.0 CPU TIMING

The Z-80 CPU executes instructions by stepping through a very precise set of a few basic operations. These include:

Memory read or write I/O device read or write Interrupt acknowledge

All instructions are merely a series of these basic operations. Each of these basic operations can take from three to six clock periods to complete or they can be lengthened to synchronize the CPU to the speed of external devices. The basic clock periods are referred to as T cycles and the basic operations are referred to as M (for machine) cycles. Figure 4.0-0 illustrates how a typical instruction will be merely a series of specific M and T cycles. Notice that this instruction consists of three machine cycles (M1, M2 and M3). The first machine cycle of any instruction is a fetch cycle which is four, five or six T cycles long (unless lengthened by the wait signal which will be fully described in the next section). The fetch cycle (M1) is used to fetch the OP code of the next instruction to be executed. Subsequent machine cycles move data between the CPU and memory or I/O devices and they may have anywhere from three to five T cycles (again they may be lengthened by wait states to synchronize the external devices to the CPU). The following paragraphs describe the timing which occurs within any of the basic machine cycles. In section 7, the exact timing for each instruction is specified.

BASIC CPU TIMING EXAMPLE FIGURE 4.0-0

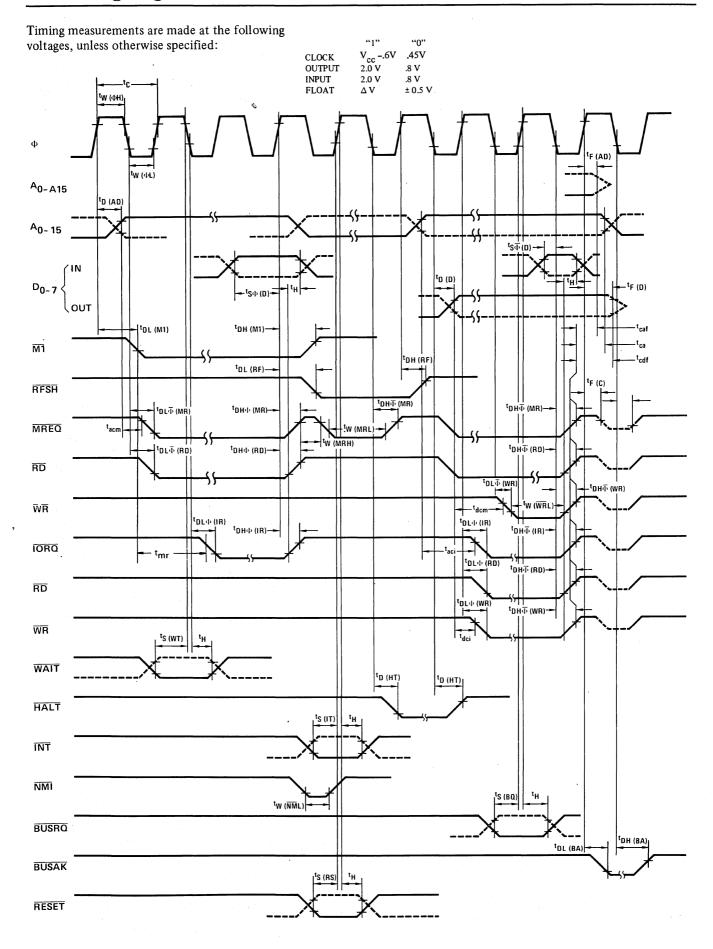

All CPU timing can be broken down into a few very simple timing diagrams as shown in figure 4.0-1 through 4.0-7. These diagrams show the following basic operations with and without wait states (wait states are added to synchronize the CPU to slow memory or I/O devices).

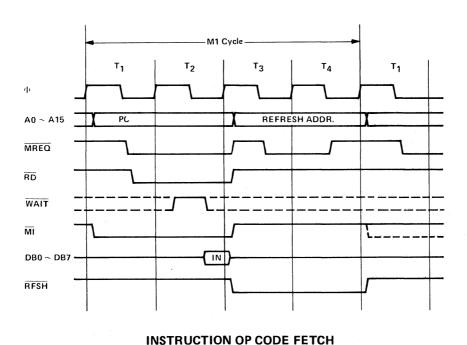

- 4.0-1. Instruction OP code fetch (M1 cycle)

- 4.0-2. Memory data read or write cycles

- 4.0-3. I/O read or write cycles

- 4.0-4. Bus Request/Acknowledge Cycle

- 4.0-5. Interrupt Request/Acknowledge Cycle

- 4.0-6. Non maskable Interrupt Request/Acknowledge Cycle

- 4.0-7. Exit from a HALT instruction

#### INSTRUCTION FETCH

Figure 4.0-1 shows the timing during an M1 cycle (OP code fetch). Notice that the PC is placed on the address bus at the beginning of the M1 cycle. One half clock time later the  $\overline{\text{MREQ}}$  signal goes active. At this time the address to the memory has had time to stabilize so that the falling edge of  $\overline{\text{MREQ}}$  can be used directly as a chip enable clock to dynamic memories. The  $\overline{\text{RD}}$  line also goes active to indicate that the memory read data should be enabled onto the CPU data bus. The CPU samples the data from the memory on the data bus with the rising edge of the clock of state T3 and this same edge is used by the CPU to turn off the  $\overline{\text{RD}}$  and  $\overline{\text{MRQ}}$  signals. Thus the data has already been sampled by the CPU before the  $\overline{\text{RD}}$  signal becomes inactive. Clock state T3 and T4 of a fetch cycle are used to refresh dynamic memories. (The CPU uses this time to decode and execute the fetched instruction so that no other operation could be performed at this time). During T3 and T4 the lower 7 bits of the address bus contain a memory refresh address and the  $\overline{\text{RFSH}}$  signal becomes active to indicate that a refresh read of all dynamic memories should be accomplished. Notice that a  $\overline{\text{RD}}$  signal is not generated during refresh time to prevent data from different memory segments from being gated onto the data bus. The  $\overline{\text{MREQ}}$  signal during refresh time should be used to perform a refresh read of all memory elements. The refresh signal can not be used by itself since the refresh address is only guaranteed to be stable during  $\overline{\text{MREQ}}$  time.

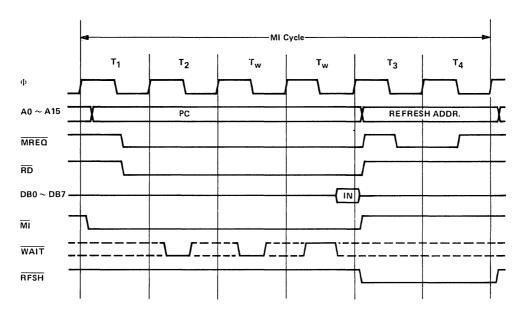

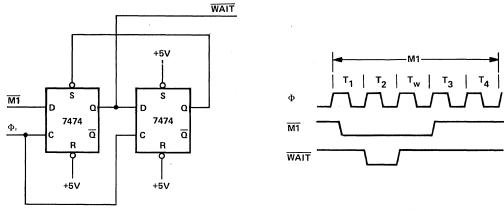

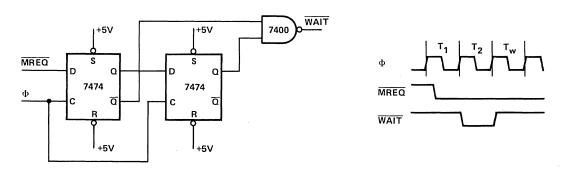

Figure 4.0-1 A illustrates how the fetch cycle is delayed if the memory activates the  $\overline{WAIT}$  line. During T2 and every subsequent Tw, the CPU samples the  $\overline{WAIT}$  line with the falling edge of  $\Phi$ . If the  $\overline{WAIT}$  line is active at this time, another wait state will be entered during the following cycle. Using this technique the read cycle can be lengthened to match the access time of any type of memory device.

**FIGURE 4.0-1**

INSTRUCTION OP CODE FETCH WITH WAIT STATES

FIGURE 4.0-1A

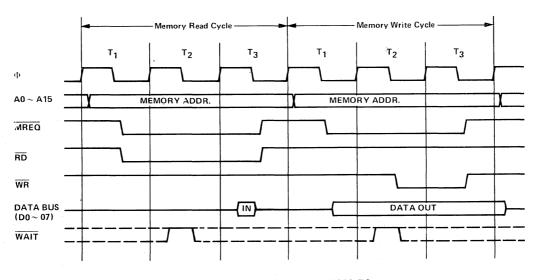

#### MEMORY READ OR WRITE

Figure 4.0-2 illustrates the timing of memory read or write cycles other than an OP code fetch (M1 cycle). These cycles are generally three clock periods long unless wait states are requested by the memory via the  $\overline{WAIT}$  signal. The  $\overline{MREQ}$  signal and the  $\overline{RD}$  signal are used the same as in the fetch cycle. In the case of a memory write cycle, the  $\overline{MREQ}$  also becomes active when the address bus is stable so that it can be used directly as a chip enable for dynamic memories. The  $\overline{WR}$  line is active when data on the data bus is stable so that it can be used directly as a R/W pulse to virtually any type of semiconductor memory. Furthermore the  $\overline{WR}$  signal goes inactive one half T state before the address and data bus contents are changed so that the overlap requirements for virtually any type of semiconductor memory type will be met.

MEMORY READ OR WRITE CYCLES FIGURE 4.0-2

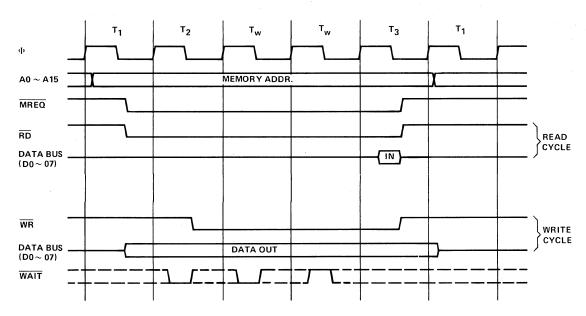

Figure 4.0-2A illustrates how a WAIT request signal will lengthen any memory read or write operation. This operation is identical to that previously described for a fetch cycle. Notice in this figure that a separate read and a separate write cycle are shown in the same figure although read and write cycles can never occur simultaneously.

MEMORY READ OR WRITE CYCLES WITH WAIT STATES

FIGURE 4.0-2A

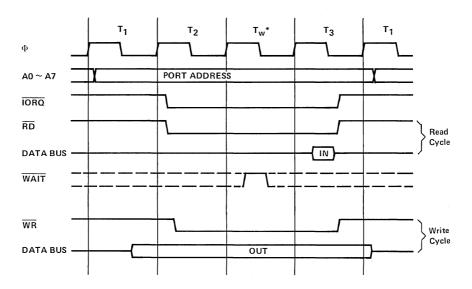

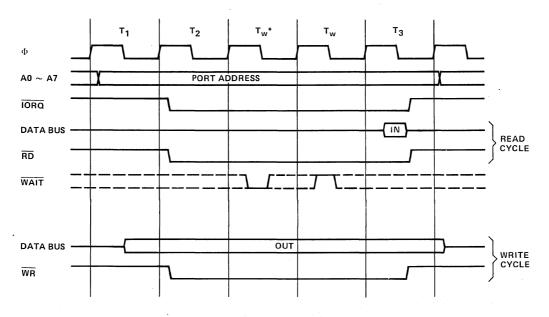

#### INPUT OR OUTPUT CYCLES

Figure 4.0-3 illustrates an I/O read or I/O write operation. Notice that during I/O operations a single wait state is automatically inserted. The reason for this is that during I/O operations, the time from when the  $\overline{IORQ}$  signal goes active until the CPU must sample the  $\overline{WAIT}$  line is very short and without this extra state sufficient time does not exist for an I/O port to decode its address and activate the  $\overline{WAIT}$  line if a wait is required. Also, without this wait state it is difficult to design MOS I/O devices that can operate at full CPU speed. During this wait state time the  $\overline{WAIT}$  request signal is sampled. During a read I/O operation, the  $\overline{RD}$  line is used to enable the addressed port onto the data bus just as in the case of a memory read. For I/O write operations, the  $\overline{WR}$  line is used as a clock to the I/O port, again with sufficient overlap timing automatically provided so that the rising edge may be used as a data clock.

Figure 4.0-3A illustrates how additional wait states may be added with the WAIT line. The operation is identical to that previously described.

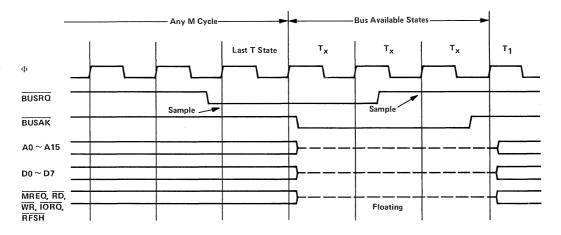

#### BUS REQUEST/ACKNOWLEDGE CYCLE

Figure 4.0-4 illustrates the timing for a Bus Request/Acknowledge cycle. The BUSRQ signal is sampled by the CPU with the rising edge of the last clock period of any machine cycle. If the BUSRQ signal is active, the CPU will set its address, data and tri-state control signals to the high impedance state with the rising edge of the next clock pulse. At that time any external device can control the buses to transfer data between memory and I/O devices. (This is generally known as Direct Memory Access [DMA] using cycle stealing). The maximum time for the CPU to respond to a bus request is the length of a machine cycle and the external controller can maintain control of the bus for as many clock cycles as is desired. Note, however, that if very long DMA cycles are used, and dynamic memories are being used, the external controller must also perform the refresh function. This situation only occurs if very large blocks of data are transferred under DMA control. Also note that during a bus request cycle, the CPU cannot be interrupted by either a  $\overline{\text{NMI}}$  or an  $\overline{\text{INT}}$  signal.

INPUT OR OUTPUT CYCLES FIGURE 4.0-3

INPUT OR OUTPUT CYCLES WITH WAIT STATES FIGURE 4.0-3A

<sup>\*</sup> Automatically inserted WAIT state

BUS REQUEST/ACKNOWLEDGE CYCLE FIGURE 4.0-4

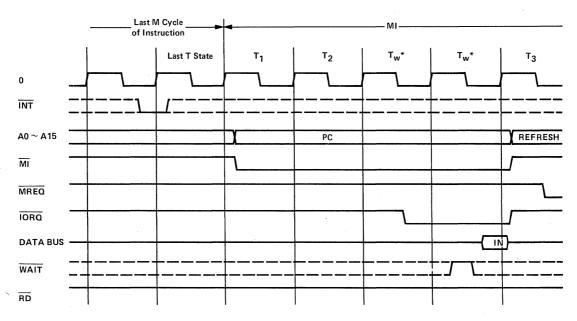

#### INTERRUPT REQUEST/ACKNOWLEDGE CYCLE

Figure 4.0-5 illustrates the timing associated with an interrupt cycle. The interrupt signal (INT) is sampled by the CPU with the rising edge of the last clock at the end of any instruction. The signal will not be accepted if the internal CPU software controlled interrupt enable flip-flop is not set or if the  $\overline{BUSRQ}$  signal is active. When the signal is accepted a special M1 cycle is generated. During this special M1 cycle the  $\overline{IORQ}$  signal becomes active (instead of the normal  $\overline{MREQ}$ ) to indicate that the interrupting device can place an 8-bit vector on the data bus. Notice that two wait states are automatically added to this cycle. These states are added so that a ripple priority interrupt scheme can be easily implemented. The two wait states allow sufficient time for the ripple signals to stabilize and identify which I/O device must insert the response vector. Refer to section 8.0 for details on how the interrupt response vector is utilized by the CPU.

INTERRUPT REQUEST/ACKNOWLEDGE CYCLE FIGURE 4.0-5

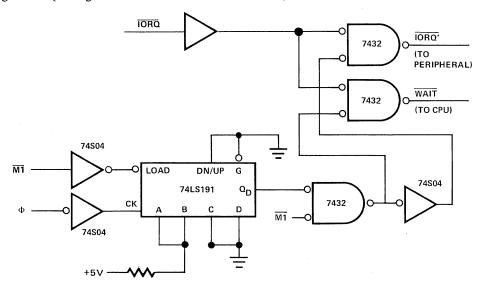

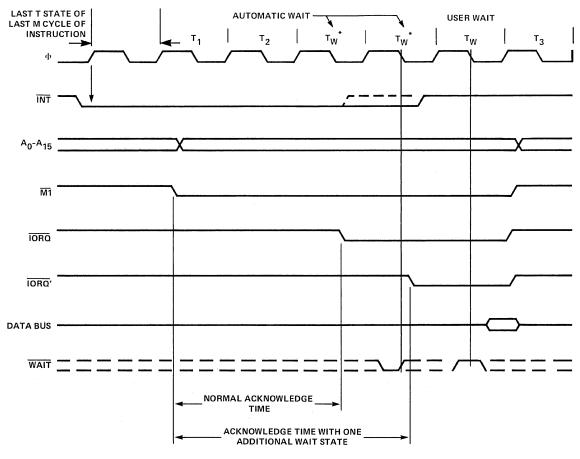

Figures 4.0-5A and 4.0-5B illustrate how a programmable counter can be used to extend interrupt acknowledge time. (Configured as shown to add one wait state)

EXTENDING INTERRUPT ACKNOWLEDGE TIME WITH WAIT STATE FIGURE 4.0-5A

REQUEST/ACKNOWLEDGE CYCLE WITH ONE ADDITIONAL WAIT STATE FIGURE 4.0-5B

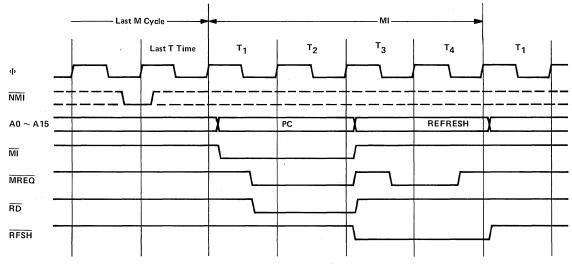

#### NON MASKABLE INTERRUPT RESPONSE

Figure 4.0-6 illustrates the request/acknowledge cycle for the non maskable interrupt. This signal is sampled at the same time as the interrupt line, but this line has priority over the normal interrupt and it can not be disabled under software control. Its usual function is to provide immediate response to important signals such as an impending power failure. The CPU response to a non maskable interrupt is similar to a normal memory read operation. The only difference being that the content of the data bus is ignored while the processor automatically stores the PC in the external stack and jumps to location 0066<sub>H</sub>. The service routine for the non maskable interrupt must begin at this location if this interrupt is used.

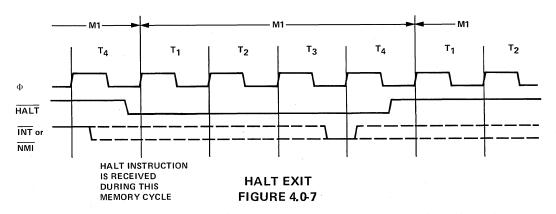

#### HALT EXIT

Whenever a software halt instruction is executed the CPU begins executing NOP's until an interrupt is received (either a non maskable or a maskable interrupt while the interrupt flip flop is enabled). The two interrupt lines are sampled with the rising clock edge during each T4 state as shown in figure 4.0-7. If a non maskable interrupt has been received or a maskable interrupt has been received and the interrupt enable flip-flop is set, then the halt state will be exited on the next rising clock edge. The following cycle will then be an interrupt acknowledge cycle corresponding to the type of interrupt that was received. If both are received at this time, then the non maskable one will be acknowledged since it has highest priority. The purpose of executing NOP instructions while in the halt state is to keep the memory refresh signals active. Each cycle in the halt state is a normal M1 (fetch) cycle except that the data received from the memory is ignored and a NOP instruction is forced internally to the CPU. The halt acknowledge signal is active during this time to indicate that the processor is in the halt state.

NON MASKABLE INTERRUPT REQUEST OPERATION FIGURE 4.0-6

#### 5.0 Z-80 CPU INSTRUCTION SET

The Z-80 CPU can execute 158 different instruction types including all 78 of the 8080A CPU. The instructions can be broken down into the following major groups:

- Load and Exchange

- Block Transfer and Search

- Arithmetic and Logical

- Rotate and Shift

- Bit Manipulation (set, reset, test)

- Jump, Call and Return

- Input/Output

- Basic CPU Control

#### 5.1 INTRODUCTION TO INSTRUCTION TYPES

The load instructions move data internally between CPU registers or between CPU registers and external memory. All of these instructions must specify a source location from which the data is to be moved and a destination location. The source location is not altered by a load instruction. Examples of load group instructions include moves between any of the general purpose registers such as move the data to Register B from Register C. This group also includes load immediate to any CPU register or to any external memory location. Other types of load instructions allow transfer between CPU registers and memory locations. The exchange instructions can trade the contents of two registers.

A unique set of block transfer instructions is provided in the Z-80. With a single instruction a block of memory of any size can be moved to any other location in memory. This set of block moves is extremely valuable when large strings of data must be processed. The Z-80 block search instructions are also valuable for this type of processing. With a single instruction, a block of external memory of any desired length can be searched for any 8-bit character. Once the character is found or the end of the block is reached, the instruction automatically terminates. Both the block transfer and the block search instructions can be interrupted during their execution so as to not occupy the CPU for long periods of time.

The arithmetic and logical instructions operate on data stored in the accumulator and other general purpose CPU registers or external memory locations. The results of the operations are placed in the accumulator and the appropriate flags are set according to the result of the operation. An example of an arithmetic operation is adding the accumulator to the contents of an external memory location. The results of the addition are placed in the accumulator. This group also includes 16-bit addition and subtraction between 16-bit CPU registers.

The rotate and shift group allows any register or any memory location to be rotated right or left with or without carry either arithmetic or logical. Also, a digit in the accumulator can be rotated right or left with two digits in any memory location.

The bit manipulation instructions allow any bit in the accumulator, any general purpose register or any external memory location to be set, reset or tested with a single instruction. For example, the most significant bit of register H can be reset. This group is especially useful in control applications and for controlling software flags in general purpose programming.

The jump, call and return instructions are used to transfer between various locations in the user's program. This group uses several different techniques for obtaining the new program counter address from specific external memory locations. A unique type of call is the restart instruction. This instruction actually contains the new address as a part of the 8-bit OP code. This is possible since only 8 separate addresses located in page zero of the external memory may be specified. Program jumps may also be achieved by loading register HL, IX or IY directly into the PC, thus allowing the jump address to be a complex function of the routine being executed.

The input/output group of instructions in the Z-80 allow for a wide range of transfers between external memory locations or the general purpose CPU registers, and the external I/O devices. In each case, the port number is provided on the lower 8 bits of the address bus during any I/O transaction. One instruction allows this port number to be specified by the second byte of the instruction while other Z-80 instructions allow it to be specified as the content of the C register. One major advantage of using the C register as a pointer to the I/O device is that it allows different I/O ports to share common software driver routines. This is not possible when the address is part of the OP code if the routines are stored in ROM. Another feature of these input instructions is that they set the flag register automatically so that additional operations are not required to determine the state of the input data (for example its parity). The Z-80 CPU includes single instructions that can move blocks of data (up to 256 bytes) automatically to or from any I/O port directly to any memory location. In conjunction with the dual set of general purpose registers, these instructions provide for fast I/O block transfer rates. The value of this I/O instruction set is demonstrated by the fact that the Z-80 CPU can provide all required floppy disk formatting (i.e., the CPU provides the preamble, address, data and enables the CRC codes) on double density floppy disk drives on an interrupt driven basis.

Finally, the basic CPU control instructions allow various options and modes. This group includes instructions such as setting or resetting the interrupt enable flip flop or setting the mode of interrupt response.

#### 5,2 ADDRESSING MODES

Most of the Z-80 instructions operate on data stored in internal CPU registers, external memory or in the I/O ports. Addressing refers to how the address of this data is generated in each instruction. This section gives a brief summary of the types of addressing used in the Z-80 while subsequent sections detail the type of addressing available for each instruction group.

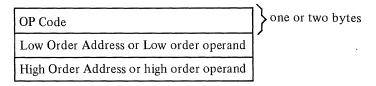

Immediate. In this mode of addressing the byte following the OP code in memory contains the actual operand.

$$\begin{pmatrix} OP Code \\ Operand \\ d_0 \end{pmatrix}$$

one or 2 bytes

Examples of this type of instruction would be to load the accumulator with a constant, where the constant is the byte immediately following the OP code.

**Immediate Extended.** This mode is merely an extension of immediate addressing in that the two bytes following the OP codes are the operand.

| OP code | one or 2 bytes |

|---------|----------------|

| Operand | low order      |

| Operand | high order     |

Examples of this type of instruction would be to load the HL register pair (16-bit register) with 16 bits (2 bytes) of data.

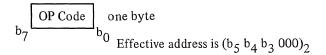

Modified Page Zero Addressing. The Z-80 has a special single byte CALL instruction to any of 8 locations in page zero of memory. This instruction (which is referred to as a restart) sets the PC to an effective address in page zero. The value of this instruction is that it allows a single byte to specify a complete 16-bit address where commonly called subroutines are located, thus saving memory space.

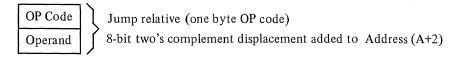

**Relative Addressing.** Relative addressing uses one byte of data following the OP code to specify a displacement from the existing program to which a program jump can occur. This displacement is a signed two's complement number that is added to the address of the OP code of the following instruction.

The value of relative addressing is that it allows jumps to nearby locations while only requiring two bytes of memory space. For most programs, relative jumps are by far the most prevalent type of jump due to the proximity of related program segments. Thus, these instructions can significantly reduce memory space requirements. The signed displacement can range between +127 and -128 from A + 2. This allows for a total displacement of +129 to -126 from the jump relative OP code address. Another major advantage is that it allows for relocatable code.

**Extended Addressing.** Extended Addressing provides for two bytes (16 bits) of address to be included in the instruction. This data can be an address to which a program can jump or it can be an address where an operand is located.

Extended addressing is required for a program to jump from any location in memory to any other location, or load and store data in any memory location.

When extended addressing is used to specify the source or destination address of an operand, the notation (nn) will be used to indicate the content of memory at nn, where nn is the 16-bit address specified in the instruction. This means that the two bytes of address nn are used as a pointer to a memory location. The use of the parentheses always means that the value enclosed within them is used as a pointer to a memory location. For example, (1200) refers to the contents of memory at location 1200.

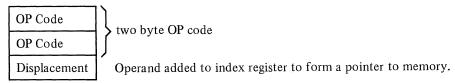

Indexed Addressing. In this type of addressing, the byte of data following the OP code contains a displacement which is added to one of the two index registers (the OP code specifies which index register is used) to form a pointer to memory. The contents of the index register are not altered by this operation.

An example of an indexed instruction would be to load the contents of the memory location (Index Register + Displacement ) into the accumulator. The displacement is a signed two's complement number. Indexed addressing greatly simplifies programs using tables of data since the index register can point to the start of any table. Two index registers are provided since very often operations require two or more tables. Indexed addressing also allows for relocatable code.

The two index registers in the Z-80 are referred to as IX and IY. To indicate indexed addressing the notation:

is used. Here d is the displacement specified after the OP code. The parentheses indicate that this value is used as a pointer to external memory.

Register Addressing. Many of the Z-80 OP codes contain bits of information that specify which CPU register is to be used for an operation. An example of register addressing would be to load the data in register B into register C.

Implied Addressing. Implied addressing refers to operations where the OP code automatically implies one or more CPU registers as containing the operands. An example is the set of arithmetic operations where the accumulator is always implied to be the destination of the results.

**Register Indirect Addressing.** This type of addressing specifies a 16-bit CPU register pair (such as HL) to be used as a pointer to any location in memory. This type of instruction is very powerful and it is used in a wide range of applications.

An example of this type of instruction would be to load the accumulator with the data in the memory location pointed to by the HL register contents. Indexed addressing is actually a form of register indirect addressing except that a displacement is added with indexed addressing. Register indirect addressing allows for very powerful but simple to implement memory accesses. The block move and search commands in the Z-80 are extensions of this type of addressing where automatic register incrementing, decrementing and comparing has been added. The notation for indicating register indirect addressing is to put parentheses around the name of the register that is to be used as the pointer. For example, the symbol

(HL)

specifies that the contents of the HL register are to be used as a pointer to a memory location. Often register indirect addressing is used to specify 16-bit operands. In this case, the register contents point to the lower order portion of the operand while the register contents are automatically incremented to obtain the upper portion of the operand.

Bit Addressing. The Z-80 contains a large number of bit set, reset and test instructions. These instructions allow any memory location or CPU register to be specified for a bit operation through one of three previous addressing modes (register, register indirect and indexed) while three bits in the OP code specify which of the eight bits is to be manipulated.

#### ADDRESSING MODE COMBINATIONS

Many instructions include more than one operand (such as arithmetic instructions or loads). In these cases, two types of addressing may be employed. For example, load can use immediate addressing to specify the source and register indirect or indexed addressing to specify the destination.

#### 5.3 INSTRUCTION OP CODES

This section describes each of the Z-80 instructions and provides tables listing the OP codes for every instruction. In each of these tables the OP codes in shaded areas are identical to those offered in the 8080A CPU. Also shown is the assembly language mnemonic that is used for each instruction. All instruction OP codes are listed in hexadecimal notation. Single byte OP codes require two hex characters while double byte OP codes require four hex characters. The conversion from hex to binary is repeated here for convenience.

| Hex |   | Binary | J | Decimal | Н | lex . |   | Binary |   | Decimal |

|-----|---|--------|---|---------|---|-------|---|--------|---|---------|

| 0   | = | 0000   | = | 0       | 8 | 8     | = | 1000   | = | 8       |

| 1   | = | 0001   | = | 1       | Ç | 9     | = | 1001   | = | 9       |

| 2   | = | 0010   | = | 2       |   | A     | = | 1010   | = | 10      |

| 3   | = | 0011   | = | 3       | ] | В     | = | 1011   | = | 11      |

| 4   | = | 0100   | = | 4       | ( | С     | = | 1100   | = | 12      |

| 5   | = | 0101   | = | 5       | ] | D     | = | 1101   | = | 13      |

| 6   | = | 0110   | = | 6       | ] | E ·   | = | 1110   | = | 14      |

| 7   | = | 0111   | = | 7       | ] | F     | = | 1111   | = | 15      |

Z-80 instruction mnemonics consist of an OP code and zero, one or two operands. Instructions in which the operand is implied have no operand. Instructions which have only one logical operand or those in which one operand is invariant (such as the Logical OR instruction) are represented by a one operand mnemonic. Instructions which may have two varying operands are represented by two operand mnemonics.

#### LOAD AND EXCHANGE

Table 5,3-1 defines the OP code for all of the 8-bit load instructions implemented in the Z-80 CPU. Also shown in this table is the type of addressing used for each instruction. The source of the data is found on the top horizontal row while the destination is specified by the left hand column. For example, load register C from register B uses the OP code 48H. In all of the tables the OP code is specified in hexadecimal notation and the 48H (=0100 1000 binary) code is fetched by the CPU from the external memory during M1 time, decoded and then the register transfer is automatically performed by the CPU.

The assembly language mnemonic for this entire group is LD, followed by the destination followed by the source (LD DEST., SOURCE). Note that several combinations of addressing modes are possible. For example, the source may use register addressing and the destination may be register indirect; such as load the memory location pointed to by register HL with the contents of register D. The OP code for this operation would be 72. The mnemonic for this load instruction would be as follows:

The parentheses around the HL means that the contents of HL are used as a pointer to a memory location. In all Z-80 load instruction mnemonics the destination is always listed first, with the source following. The Z-80 assembly language has been defined for ease of programming. Every instruction is self documenting and programs written in Z-80 language are easy to maintain.

Note in table 5.3-1 that some load OP codes that are available in the Z-80 use two bytes. This is an efficient method of memory utilization since 8, 16, 24 or 32 bit instructions are implemented in the Z-80. Thus often utilized instructions such as arithmetic or logical operations are only 8-bits which results in better memory utilization than is achieved with fixed instruction sizes such as 16-bits.

All load instructions using indexed addressing for either the source or destination location actually use three bytes of memory with the third byte being the displacement d. For example a load register E with the operand pointed to by IX with an offset of +8 would be written:

$$LD E, (IX + 8)$$

The instruction sequence for this in memory would be:

The two extended addressing instructions are also three byte instructions. For example the instruction to load the accumulator with the operand in memory location 6F32H would be written:

and its instruction sequence would be:

Notice that the low order portion of the address is always the first operand.

The load immediate instructions for the general purpose 8-bit registers are two-byte instructions. The instruction load register H with the value 36H would be written:

and its sequence would be:

Loading a memory location using indexed addressing for the destination and immediate addressing for the source requires four bytes. For example:

would appear as:

Notice that with any indexed addressing the displacement always follows directly after the OP code.

Table 5.3-2 specifies the 16-bit load operations. This table is very similar to the previous one. Notice that the extended addressing capability covers all register pairs. Also notice that register indirect operations specifying the stack pointer are the PUSH and POP instructions. The mnemonic for these instructions is "PUSH" and "POP." These differ from other 16-bit loads in that the stack pointer is automatically decremented and incremented as each byte is pushed onto or popped from the stack respectively. For example the instruction:

PUSH AF

is a single byte instruction with the OP code of F5H. When this instruction is executed the following sequence is generated:

Decrement SP LD (SP), A Decrement SP LD (SP), F

Thus the external stack now appears as follows:

|            |                 |        | SOURCE |          |               |               |               |               |               |               |               |      |       |      |               |               |                                         |               |

|------------|-----------------|--------|--------|----------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|------|-------|------|---------------|---------------|-----------------------------------------|---------------|

|            |                 |        | IMP    | LIED     |               |               | F             | REGISTE       | R             |               |               | REC  | INDIR | ЕСТ  | IND           | EXED          | EXT.<br>ADDR.                           | IMME.         |

|            |                 |        | 1      | R        | Α             | В             | С             | D             | E             | н             | L             | (HL) | (BC)  | (DE) | (IX + d)      | (1Y + d)      | (nn)                                    | n             |

|            |                 | A      | ED 57  | ED<br>5F | 7F            | 78            | 79            | 7A            | 7B            | 7C            | 70            | 7E   | 0A    | 14   | DD<br>7E<br>d | FD<br>7E<br>d | 3A<br>n<br>n                            | 3E<br>n       |

|            |                 | В      |        |          | 47            | 40            | 41            | 42            | 43            | 44            | 45            | 46   |       |      | DD<br>46<br>d | FD<br>46<br>d | *************************************** | 06<br>n       |

|            |                 | С      |        |          | 4F            | 48            | 49            | 4A            | 48            | 4C            | 4D            | 4E   |       |      | DD<br>4E<br>d | FD<br>4E<br>d |                                         | OE<br>n       |

|            | REGISTER        | D      |        |          | 57            | 50            | 51            | 52            | 53            | 54            | 55            | 56   |       |      | DD<br>56<br>d | FD<br>56<br>d |                                         | 16<br>n       |

|            |                 | E      |        |          | 5F            | 58            | 59            | 5A            | 5B            | 5C            | 5D            | 5E   |       | i    | DD<br>5E<br>d | FD<br>5E<br>d |                                         | 1E<br>n       |

|            |                 | н      |        |          | 67            | 60            | 61            | 62            | 63            | 64            | 65            | 66   |       |      | DD<br>66<br>d | FD<br>66<br>d |                                         | 26<br>n       |

|            |                 | L      |        |          | 6F            | 68            | 69            | 6A            | 6B            | 6C            | 6D            | 6E   |       |      | DD<br>6E<br>d | FD<br>6E<br>d |                                         | 2E<br>n       |

| ESTINATION |                 | (HL)   |        |          | 77            | 70            | 71            | 72            | 73            | 74            | 75            |      |       |      |               |               |                                         | 36<br>n       |

|            | REG<br>INDIRECT | (BC)   |        |          | 02            |               |               |               |               |               |               |      |       |      |               |               |                                         |               |

|            |                 | (DE)   | ,      |          | 12            |               |               |               |               |               |               |      |       |      |               |               |                                         |               |

|            |                 | (IX+d) |        |          | DD<br>77<br>d | DD<br>70<br>d | DD<br>71<br>d | DD<br>72<br>d | DD<br>73<br>d | DD<br>74<br>d | DD<br>75<br>d |      |       |      |               |               |                                         | DD<br>36<br>d |

|            | INDEXED         | (IY+d) |        |          | FD<br>77<br>d | FD<br>70<br>d | FD<br>71<br>d | FD<br>72<br>d | FD<br>73<br>d | FD<br>74<br>d | FD<br>75<br>d |      |       |      |               |               |                                         | FD<br>36<br>d |

|            | EXT. ADDR       | (nn)   |        |          | 32<br>n<br>n  |               |               |               |               |               |               |      |       |      |               |               |                                         |               |

|            |                 | t      |        |          | ED<br>47      |               |               |               |               |               |               |      |       |      |               |               |                                         |               |

|            | IMPLIED         | R      |        |          | ED<br>4F      |               | -             |               |               |               |               |      |       |      |               |               |                                         |               |

8 BIT LOAD GROUP 'LD' TABLE 5.3-1 The POP instruction is the exact reverse of a PUSH. Notice that all PUSH and POP instructions utilize a 16-bit operand and the high order byte is always pushed first and popped last. That is a:

PUSH BC is PUSH B then C

PUSH DE is PUSH D then E

PUSH HL is PUSH H then-L

POP HL is POP L then H

The instruction using extended immediate addressing for the source obviously requires 2 bytes of data following the OP code. For example:

LD DE, 0659H

will be:

| Address A | 11 | OP Code                          |

|-----------|----|----------------------------------|

| A+1       | 59 | Low order operand to register E  |

| A+2       | 06 | High order operand to register D |

In all extended immediate or extended addressing modes, the low order byte always appears first after the OP code.

Table 5.3-3 lists the 16-bit exchange instructions implemented in the Z-80. OP code 08H allows the programmer to switch between the two pairs of accumulator flag registers while D9H allows the programmer to switch between the duplicate set of six general purpose registers. These OP codes are only one byte in length to absolutely minimize the time necessary to perform the exchange so that the duplicate banks can be used to effect very fast interrupt response times.

#### **BLOCK TRANSFER AND SEARCH**

Table 5.3-4 lists the extremely powerful block transfer instructions. All of these instructions operate with three registers.

HL points to the source location.

DE points to the destination location.

BC is a byte counter.

After the programmer has initialized these three registers, any of these four instructions may be used. The LDI (Load and Increment) instruction moves one byte from the location pointed to by HL to the location pointed to by DE. Register pairs HL and DE are then automatically incremented and are ready to point to the following locations. The byte counter (register pair BC) is also decremented at this time. This instruction is valuable when blocks of data must be moved but other types of processing are required between each move. The LDIR (Load, increment and repeat) instruction is an extension of the LDI instruction. The same load and increment operation is repeated until the byte counter reaches the count of zero. Thus, this single instruction can move any block of data from one location to any other.

Note that since 16-bit registers are used, the size of the block can be up to 64K bytes (1K = 1024) long and it can be moved from any location in memory to any other location. Furthermore the blocks can be overlapping since there are absolutely no constraints on the data that is used in the three register pairs.

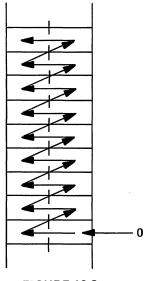

The LDD and LDDR instructions are very similar to the LDI and LDIR. The only difference is that register pairs HL and DE are decremented after every move so that a block transfer starts from the highest address of the designated block rather than the lowest.

#### SOURCE

|                   | REGISTER      |      |    |                    |               |              | IMM.<br>EXT.       | EXT.<br>ADDR. | REG.<br>INDIR.     |               |                    |          |

|-------------------|---------------|------|----|--------------------|---------------|--------------|--------------------|---------------|--------------------|---------------|--------------------|----------|

|                   |               |      | AF | вс                 | DE            | HL           | SP                 | ıx            | IY                 | nn            | (nn)               | (SP)     |

|                   |               | AF   |    |                    |               |              |                    |               |                    |               |                    | F1       |

|                   |               | ВС   |    |                    |               |              |                    |               |                    | 01<br>n<br>n  | ED<br>4B<br>n      | C1 54    |

|                   | EG            | DE   |    |                    |               |              |                    |               |                    | 11<br>n<br>n  | ED<br>5B<br>n      | D1       |

| DESTINATION       |               | HL   |    |                    |               |              |                    | !             |                    | 21<br>n<br>n  | 2A<br>n<br>n       | E1       |

| ,                 |               | SP   |    |                    |               | F9           |                    | DD<br>F9      | FD<br>F9           | 31<br>n<br>n  | ED<br>7B<br>n      |          |

|                   |               | IX   |    |                    |               |              |                    |               |                    | DD<br>21<br>n | DD<br>2A<br>n      | DD<br>E1 |

|                   |               | IY   |    |                    |               |              |                    |               |                    | FD<br>21<br>n | FD<br>2A<br>n<br>n | FD<br>E1 |

|                   | EXT.<br>ADDR. | (nn) |    | ED<br>43<br>n<br>n | ED<br>53<br>n | 22<br>n<br>n | ED<br>73<br>n<br>n | DD<br>22<br>n | FD<br>22<br>n<br>n |               |                    |          |

| PUSH INSTRUCTIONS | REG.<br>IND.  | (SP) | F5 | C5                 | D5            | <b>E</b> 5   |                    | DD<br>E5      | FD<br>E5           |               |                    |          |

NOTE: The Push & Pop Instructions adjust the SP after every execution

POP INSTRUCTIONS

16 BIT LOAD GROUP 'LD' 'PUSH' AND 'POP' TABLE 5.3-2

|                |                      |                 | IMPLIED ADDRESSING |    |          |          |  |  |  |

|----------------|----------------------|-----------------|--------------------|----|----------|----------|--|--|--|

|                |                      | AF <sup>'</sup> | BC, DE & HL        | IX | ΙΥ       |          |  |  |  |

|                | AF                   | 08              |                    |    |          |          |  |  |  |

| IMPLIED        | BC,<br>DE<br>&<br>HL |                 | D9                 |    |          |          |  |  |  |

|                | DE                   |                 |                    | EB |          |          |  |  |  |

| REG.<br>INDIR. | (SP)                 |                 |                    | E3 | DD<br>E3 | FD<br>E3 |  |  |  |

EXCHANGES 'EX' AND 'EXX' TABLE 5.3-3

|                |                |      | REG.<br>INDIR. |                                                                                  |

|----------------|----------------|------|----------------|----------------------------------------------------------------------------------|

|                |                |      | ED<br>A0       | 'LDI' - Load (DE) - (HL)<br>Inc HL & DE, Dec BC                                  |

| DECEMBER TO AN | REG.<br>INDIR. |      | ED<br>B0       | 'LDIR,' — Load (DE)                                                              |

| DESTINATION    |                | (DE) | ED<br>A8       | 'LDD' — Load (DE) <del>←</del> (HL)<br>Dec HL & DE, Dec BC                       |

|                |                | - ;  | ED<br>B8       | 'LDDR' — Load (DE) <del>—</del> (HL)<br>Dec HL & DE, Dec BC, Repeat until BC = 0 |

Reg HL points to source

Reg DE points to destination

Reg BC is byte counter

#### BLOCK TRANSFER GROUP TABLE 5.3-4

Table 5.3-5 specifies the OP codes for the four block search instructions. The first, CPI (compare and increment) compares the data in the accumulator, with the contents of the memory location pointed to by register HL. The result of the compare is stored in one of the flag bits (see section 6.0 for a detailed explanation of the flag operations) and the HL register pair is then incremented and the byte counter (register pair BC) is decremented.

The instruction CPIR is merely an extension of the CPI instruction in which the compare is repeated until either a match is found or the byte counter (register pair BC) becomes zero. Thus, this single instruction can search the entire memory for any 8-bit character.

The CPD (Compare and Decrement) and CPDR (Compare, Decrement and Repeat) are similar instructions, their only difference being that they decrement HL after every compare so that they search the memory in the opposite direction. (The search is started at the highest location in the memory block).

It should be emphasized again that these block transfer and compare instructions are extremely powerful in string manipulation applications.

#### ARITHMETIC AND LOGICAL

Table 5.3-6 lists all of the 8-bit arithmetic operations that can be performed with the accumulator, also listed are the increment (INC) and decrement (DEC) instructions. In all of these instructions, except INC and DEC, the specified 8-bit operation is performed between the data in the accumulator and the source data specified in the table. The result of the operation is placed in the accumulator with the exception of compare (CP) that leaves the accumulator unaffected. All of these operations affect the flag register as a result of the specified operation. (Section 6.0 provides all of the details on how the flags are affected by any instruction type). INC and DEC instructions specify a register or a memory location as both source and destination of the result. When the source operand is addressed using the index registers the displacement must follow directly. With immediate addressing the actual operand will follow directly. For example the instruction:

AND 07H

would appear as:

| SEARCH<br>LOCATIO |                                                          |

|-------------------|----------------------------------------------------------|

| REG.<br>INDIR.    |                                                          |

| (HL)              | ·                                                        |

| ED<br>A1          | 'CPI'<br>Inc HL, Dec BC                                  |

| ED<br>B1          | 'CPIR', Inc HL, Dec BC repeat until BC = 0 or find match |

| ED<br>A9          | 'CPD' Dec HL & BC                                        |

| ED<br>B9          | 'CPDR' Dec HL & BC<br>Repeat until BC = 0 or find match  |

HL points to location in memory to be compared with accumulator contents BC is byte counter

#### BLOCK SEARCH GROUP TABLE 5.3-5

Assuming that the accumulator contained the value F3H the result of 03H would be placed in the accumulator:

| Acc before operation | $1111\ 0011 = F3H$ |

|----------------------|--------------------|

| Operand              | $0000\ 0111 = 07H$ |

| Result to Acc        | $0000\ 0011 = 03H$ |

The Add instruction (ADD) performs a binary add between the data in the source location and the data in the accumulator. The subtract (SUB) does a binary subtraction. When the add with carry is specified (ADC) or the subtract with carry (SBC), then the carry flag is also added or subtracted respectively. The flags and decimal adjust instruction (DAA) in the Z-80 (fully described in section 6.0) allow arithmetic operations for:

multiprecision packed BCD numbers

multiprecision signed or unsigned binary numbers

multiprecision two's complement signed numbers

Other instructions in this group are logical and (AND), logical or (OR), exclusive or (XOR) and compare (CP).

There are five general purpose arithmetic instructions that operate on the accumulator or carry flag. These five are listed in table 5.3-7. The decimal adjust instruction can adjust for subtraction as well as addition, thus making BCD arithmetic operations simple. Note that to allow for this operation the flag N is used. This flag is set if the last arithmetic operation was a subtract. The negate accumulator (NEG) instruction forms the two's complement of the number in the accumulator. Finally notice that a reset carry instruction is not included in the Z-80 since this operation can be easily achieved through other instructions such as a logical AND of the accumulator with itself.

Table 5.3-8 lists all of the 16-bit arithmetic operations between 16-bit registers. There are five groups of instructions including add with carry and subtract with carry. ADC and SBC affect all of the flags. These two groups simplify address calculation operations or other 16-bit arithmetic operations.

SOURCE

|                      | REGISTER ADDRESSING |    |    |    |    |    |            |      | INDEXED         |               | IMMED.  |

|----------------------|---------------------|----|----|----|----|----|------------|------|-----------------|---------------|---------|

|                      | Α                   | В  | С  | D  | E  | Н  | L          | (HL) | (IX+d)          | (IY+d)        | n       |

| 'ADD'                | 87                  | 80 | 81 | 82 | 83 | 84 | 85         | 86   | DD<br>86<br>d   | FD<br>86<br>d | C6      |

| ADD w CARRY<br>'ADC' | 8F                  | 88 | 89 | 8A | 8B | 8C | 8D         | 8E   | DD<br>8E<br>d   | FD<br>8E<br>d | CE<br>n |

| SUBTRACT<br>'SUB'    | 97                  | 90 | 91 | 92 | 93 | 94 | 95         | 96   | DD<br>96<br>d   | FD<br>96<br>d | D6<br>n |

| SUB w CARRY<br>'SBC' | 9F                  | 98 | 99 | 9A | 9B | 9C | 9D         | 9E   | DD<br>9E<br>d   | FD<br>9E<br>d | DE<br>n |

| 'AND'                | A7                  | Α0 | A1 | A2 | АЗ | A4 | <b>A</b> 5 | A6   | DD /<br>A6<br>d | FD<br>A6<br>d | E6      |

| 'XOR'                | AF                  | A8 | A9 | AA | АВ | AC | AD         | AE   | DD<br>AE<br>d   | FD<br>AE<br>d | EE<br>n |

| 'OR'                 | В7                  | В0 | B1 | B2 | В3 | B4 | B5         | B6   | DD<br>B6<br>d   | FD<br>B6<br>d | F6      |

| COMPARE<br>'CP'      | BF                  | B8 | В9 | ВА | ВВ | вс | BD         | BE   | DD<br>BE<br>d   | FD<br>BE<br>d | FE<br>n |

| INCREMENT<br>'INC'   | 3C                  | 04 | 0C | 14 | 1C | 24 | 2C         | 34   | DD<br>34<br>d   | FD<br>34<br>d |         |

| DECREMENT<br>'DEC'   | . 3D                | 05 | 0D | 15 | 1D | 25 | 2D         | 35   | DD<br>35<br>d   | FD<br>35<br>d |         |

# 8 BIT ARITHMETIC AND LOGIC TABLE 5.3-6

| Decimal Adjust Acc, 'DAA'             | 27       |

|---------------------------------------|----------|

| Complement Acc, 'CPL'                 | 2F       |

| Negate Acc, 'NEG'<br>(2's complement) | ED<br>44 |

| Complement Carry Flag, 'CCF'          | 3F       |

| Set Carry Flag, 'SCF'                 | 37       |

# GENERAL PURPOSE AF OPERATIONS TABLE 5.3-7

#### SOURCE

|                    |                                       | 1  |          |          |          |          |          |          |

|--------------------|---------------------------------------|----|----------|----------|----------|----------|----------|----------|

|                    |                                       |    | вс       | DE       | HL       | SP       | ıx       | IY       |

| <b>DESTINATION</b> |                                       | HL | 09       | 19       | 29       | 39       |          |          |

|                    | 'ADD'                                 | IX | DD<br>09 | DD<br>19 |          | DD<br>39 | DD<br>29 |          |

|                    |                                       | IY | FD<br>09 | FD<br>19 |          | FD<br>39 |          | FD<br>29 |

|                    | ADD WITH CARRY AND<br>SET FLAGS 'ADC' | HL | ED<br>4A | ED<br>5A | ED<br>6A | ED<br>7A |          |          |

|                    | SUB WITH CARRY AND<br>SET FLAGS 'SBC' | HL | ED<br>42 | ED<br>52 | ED<br>62 | ED<br>72 |          |          |

|                    | INCREMENT 'INC                        | ;' | 03       | 13       | 23       | 33       | DD<br>23 | FD<br>23 |

|                    | DECREMENT 'DE                         | C' | ОВ       | 1B       | 2B       | 3B       | DD<br>2B | FD<br>2B |

### 16 BIT ARITHMETIC TABLE 5.3–8

#### **ROTATE AND SHIFT**

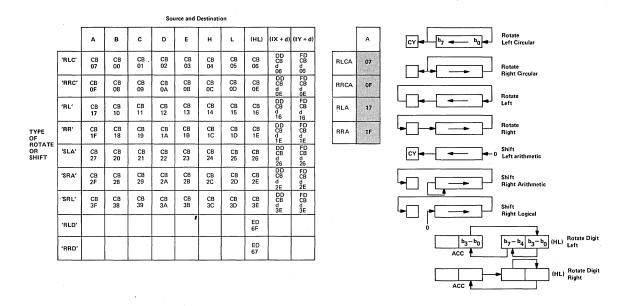

A major capability of the Z-80 is its ability to rotate or shift data in the accumulator, any general purpose register, or any memory location. All of the rotate and shift OP codes are shown in table 5.3-9. Also included in the Z-80 are arithmetic and logical shift operations. These operations are useful in an extremely wide range of applications including integer multiplication and division. Two BCD digit rotate instructions (RRD and RLD) allow a digit in the accumulator to be rotated with the two digits in a memory location pointed to by register pair HL. (See figure 5.3-9). These instructions allow for efficient BCD arithmetic.

#### **BIT MANIPULATION**

The ability to set, reset and test individual bits in a register or memory location is needed in almost every program. These bits may be flags in a general purpose software routine, indications of external control conditions or data packed into memory locations to make memory utilization more efficient.

The Z-80 has the ability to set, reset or test any bit in the accumulator, any general purpose register or any memory location with a single instruction. Table 5.3-10 lists the 240 instructions that are available for this purpose. Register addressing can specify the accumulator or any general purpose register on which the operation is to be performed. Register indirect and indexed addressing are available to operate on external memory locations. Bit test operations set the zero flag (Z) if the tested bit is a zero. (Refer to section 6.0 for further explanation of flag operation).

#### JUMP, CALL AND RETURN

Figure 5.3-11 lists all of the jump, call and return instructions implemented in the Z-80 CPU. A jump is a branch in a program where the program counter is loaded with the 16-bit value as specified by one of the three available addressing modes (Immediate Extended, Relative or Register Indirect). Notice that the jump group has several different conditions that can be specified to be met before the jump will be made. If these conditions are not met, the program merely continues with the next sequential instruction. The conditions are all dependent on the data in the flag register. (Refer to section 6.0 for details on the flag register). The immediate extended addressing is used to jump to any location in the memory. This instruction requires three bytes (two to specify the 16-bit address) with the low order address byte first followed by the high order address byte.

#### ROTATES AND SHIFTS TABLE 5.3-9

For example an unconditional Jump to memory location 3E32H would be:

| · · · · · · · · · · · · · · · · · · · |    | i                  |

|---------------------------------------|----|--------------------|

| Address A                             | С3 | OP Code            |

| A+1                                   | 32 | Low order address  |

| A+2                                   | 3E | High order address |

The relative jump instruction uses only two bytes, the second byte is a signed two's complement displacement from the existing PC. This displacement can be in the range of +129 to -126 and is measured from the address of the instruction OP code.

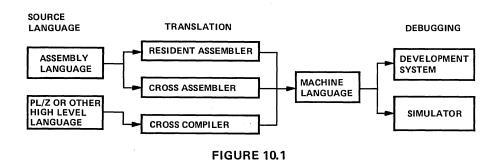

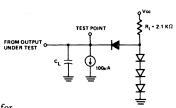

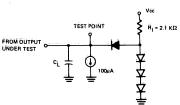

Three types of register indirect jumps are also included. These instructions are implemented by loading the register pair HL or one of the index registers IX or IY directly into the PC. This capability allows for program jumps to be a function of previous calculations.