#### **Description:**

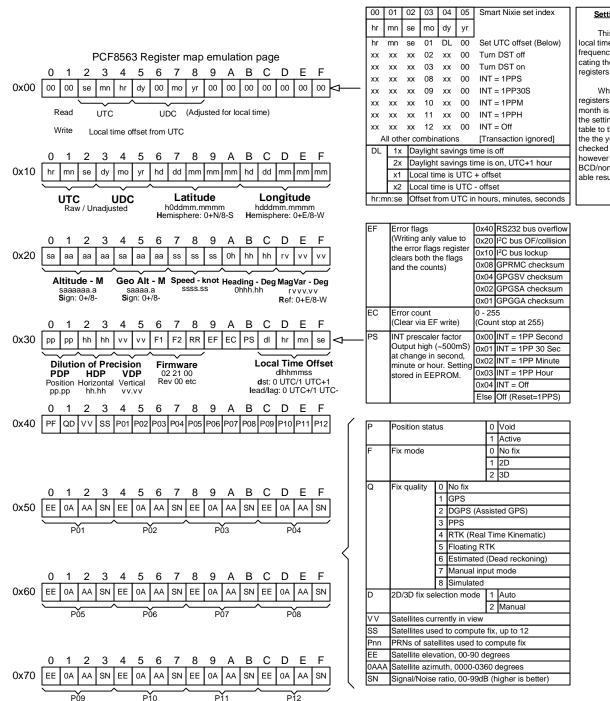

The 1375/1455 series modules are complete real time clocks (RTC) that use GPS data and a user supplied local time offset to replicate the register set of the NXP PCF8563 IC so that they can function as drop in replacements for the 1374/1362 RTC modules from TES. Additionally, the full GPS data from the GPGGA, GPGSA, GPGSV and GPRMC NMEA sentences is decoded on the fly to populate a 128 byte I<sup>2</sup>C register map with full navigational data. The PPS output is accurate to +/-1ppm.

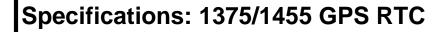

The RTC data interface is a standard I<sup>2</sup>C bus operating at 100kbps. The RTC/Slave side of the interface operates at an internal 3.3V regulated from the master side (VDD) input voltage from 3.3V to 5.5V. The master to slave I<sup>2</sup>C interface is level shifted and includes master side bus pull up resistors of 2.21K. All inputs and outputs are ESD protected (See notes on Table 2). Slave addressing information can be found in Fig. 8 and 9.

The local time offset from UTC can be entered directly into the offset registers or can be set indirectly via a time setting function, such as is used in the TES SmartNixie clock backplane. The offset can be plus or minus 23h 59m 59s in 1s increments from UTC. A one hour positive offset function for DST is also included. Local time is computed from the GPS UTC and UDC data at the end of every second and includes date adjustments for leap years. DST can be turned on and off with a short clock set sequence or programmed directly as part of the local time offset.

Once a GPS fix has been established, the battery backed internal RTC will keep time for up to three months with +/-20ppm accuracy with the power off or no GPS fix. Satellite data is stored in battery backed RAM to speed fix acquisition after brief power or satellite view interruptions.

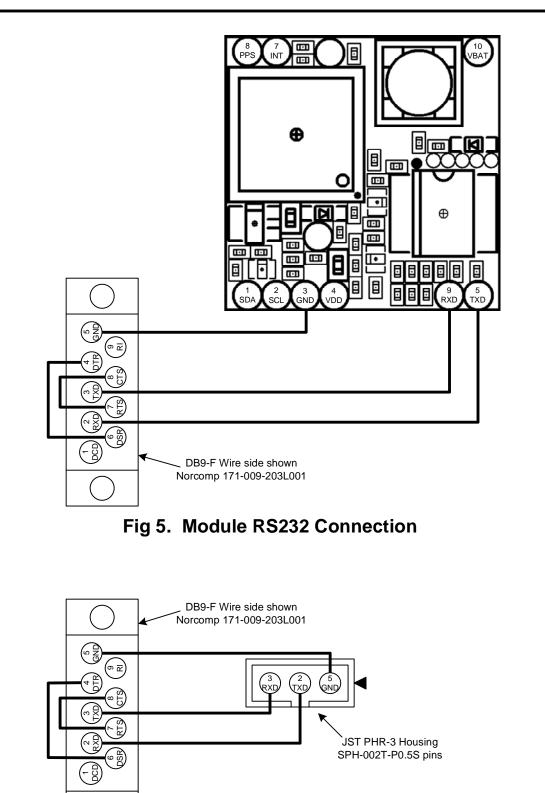

An interrupt output (INT) can be set to pulse high for 560mS every second (1PPS), 30 seconds (1PP30S), minute (1PPM), hour (1PPH) or off, The INT goes high after the GPS data has been fully decoded and the local time calculation has been completed (Useful to control slave clocks). INT is low during NMEA sentence reception and then high during RS232 idle.

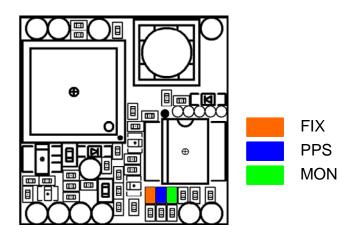

Three lamps indicate the status of the module: FIX blinks at 10Hz when the GPS indicates no fix is available, 2Hz if the fix signal is toggling faster than once per two seconds and solid on when a stable fix is indicated. PPS blinks at 1Hz 50% duty when the GPS PPS is stable at 1Hz 10% duty. MON blinks at 5Hz all the time and signals the main processing loop is running.

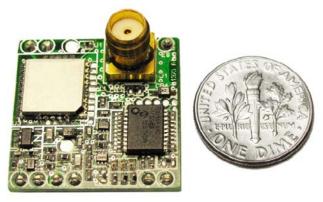

Fig 1. 1375 horizontal GPS RTC

# Taylor Electronics Services www.tayloredge.com

| Revision History |     |         |                                                                              |  |  |  |

|------------------|-----|---------|------------------------------------------------------------------------------|--|--|--|

| Date             | FW  | Affects | Description                                                                  |  |  |  |

| 2012/08/05       | All | All     | Initial release.                                                             |  |  |  |

| 2012/09/03       | All | Table 4 | Direct write prescale (PS) section updated with 1PP30S and nn > Off behavior |  |  |  |

| 2012/09/05       | All | Various | Typographical cleanup                                                        |  |  |  |

# Taylor Electronics Services www.tayloredge.com

### Table 1: GPS Receiver specifications

| Receiver                          | GPS L1 C/A-code, SPS                                                |                                              |  |

|-----------------------------------|---------------------------------------------------------------------|----------------------------------------------|--|

| Chip set                          | Mediatek MT3339                                                     |                                              |  |

| Channels                          | 66/22 (search/track)                                                |                                              |  |

| Tracking sensitivity              | -165 dBm typ.                                                       |                                              |  |

| Navigation sensitivity            | -165 dBm typ.                                                       |                                              |  |

| Navigation sensitivity, re-acq.   | -160 dBm typ.                                                       |                                              |  |

| Navigation sensitivity, cold acq. | -148 dBm typ.                                                       |                                              |  |

| External RF amp net gain range    | 0 to +30 dB                                                         |                                              |  |

| Antenna type                      | This module requires an active antenna, 3.3V nominal                |                                              |  |

| Update rate                       | 1 Hz                                                                |                                              |  |

| Position accuracy                 | 3.0 m (67%) typ. Horizontal                                         |                                              |  |

|                                   | 5.0 m (67%) typ. Vertical                                           |                                              |  |

|                                   | 0.02 m/s (50%) typ. Velocity                                        |                                              |  |

| Max altitude/velocity             | <60,000 ft/<1,000 knots                                             | (With nominal GPS<br>signal levels -130dBm.) |  |

| Time to First Fix, cold acq.      | 31 s typ.                                                           |                                              |  |

| Time to First Fix, warm acq.      | 31 s typ.                                                           |                                              |  |

| Time to First Fix, hot acq.       | 1 s typ.                                                            |                                              |  |

| Power consumption, Full Power     | 35 mW typ. @ 3.3 V (11mA)                                           | <12 GPS satellites in track                  |  |

| Power consumption, Backup         | 15 μW typ. @ 3.0 V (4.5uA)                                          |                                              |  |

| Host port protocol                | NMEA-0183 rev. 3.01                                                 |                                              |  |

| Serial data format                | 8 bits, no parity, 1 stop bit                                       |                                              |  |

| Serial data speed                 | 9600 baud                                                           |                                              |  |

| PPS output                        | 100 ms high pulse, rising edge +/-1 $\mu s$ @ full second GPS epoch |                                              |  |

Taylor Electronics Services www.tayloredge.com

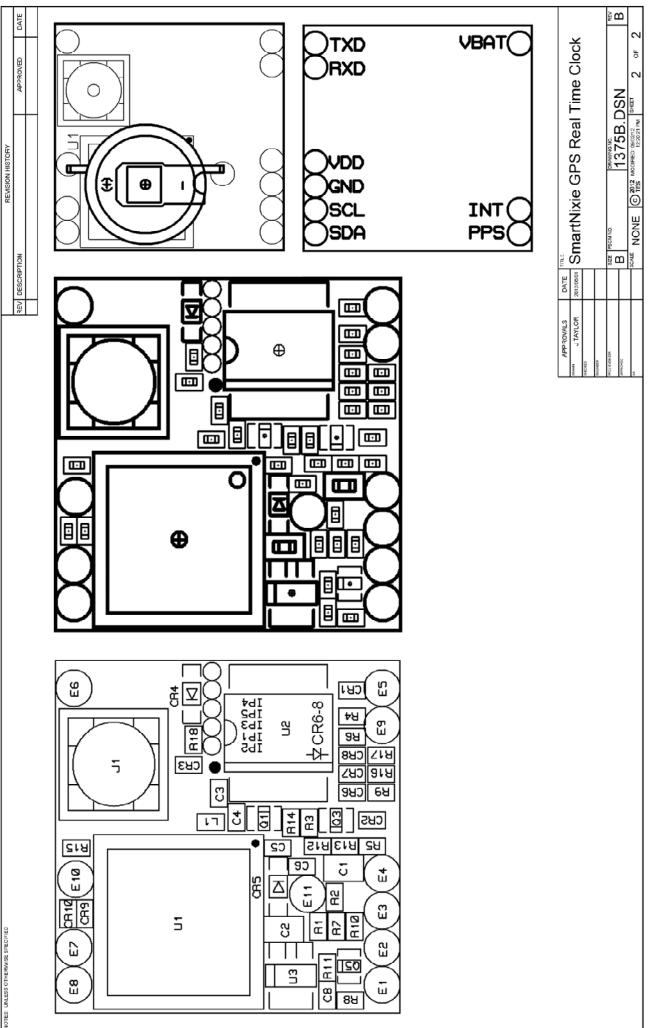

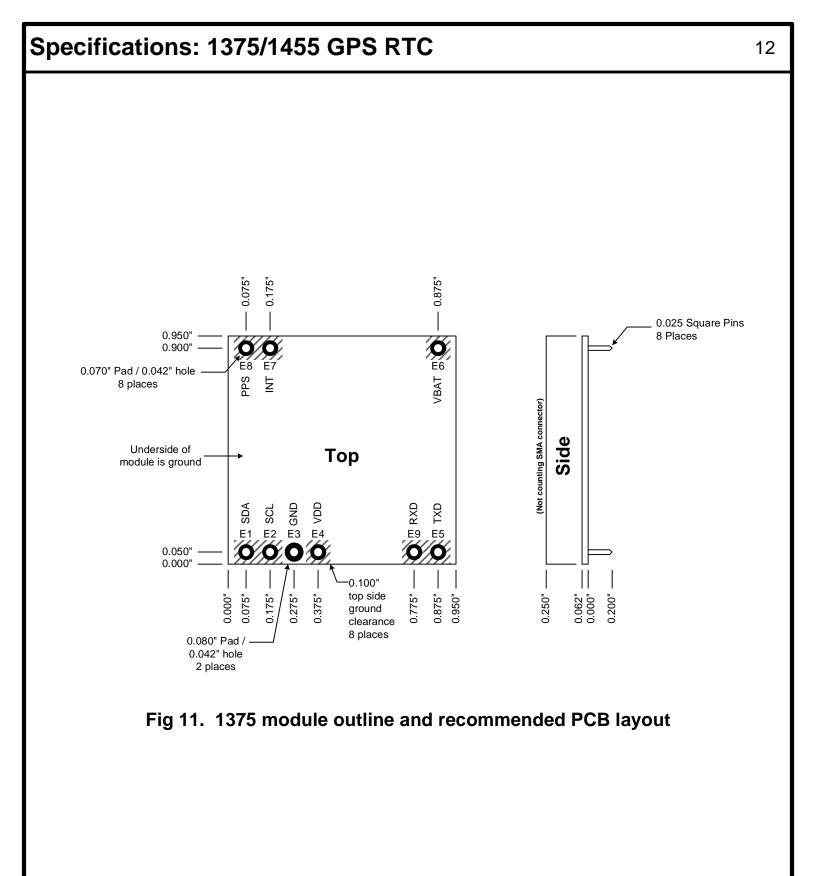

| Pin | Name | Description                                                      |

|-----|------|------------------------------------------------------------------|

| E1  | SDA  | I <sup>2</sup> C serial data. Level shifted                      |

| E2  | SCL  | I <sup>2</sup> C serial clock. Level shifted                     |

| E3  | GND  | Power return                                                     |

| E4  | VDD  | 3.3V to 5.5V power input. I <sup>2</sup> C master side reference |

| E5  | TXD  | PC logic (Idle state is low) RS232 out from GPS, 0V-VDD          |

| E6  | VBAT | Test pin for backup battery, do not connect to user circuit      |

| E7  | INT  | Active high interrupt on time update                             |

| E8  | PPS  | 100mS high pulse from GPS, +/-1ppm accuracy (GPS fix)            |

| E9  | RXD  | PC logic (Idle state is low) RS232 in to GPS, 0V-VDD             |

| SMA | RFIN | GPS RF input, passive or active (3.3V) antenna                   |

#### Table 2: Interface connector signals, horizontal module

#### Notes:

- 1. I<sup>2</sup>C SDA and SCL are ESD protected to 2KV.

- 2. INT, PPS, TXD, RXD and RFIN are ESD protected to 20KV.

- Absolute max input of VDD is 12V, limited by the level shifter transistor gates. Note that SDA and SCL are pulled up to VDD through 2.21K resistors so that SDA and SCL will equal VDD when inactive. The TXD output is also pulled up to VDD via a 2.21K resistor but is voltage limited by its ESD protection ~6V.

- 4. PPS and INT output current is +/-10mA max.

- VBAT may be measured to check the charge state of the battery, where the charge current is (3.3V - VBAT) / 249ohms when VDD is >3.4V. Otherwise, charge/discharge current can be measured across R15.

Fig 3. Status lamp locations

Taylor Electronics Services www.tayloredge.com

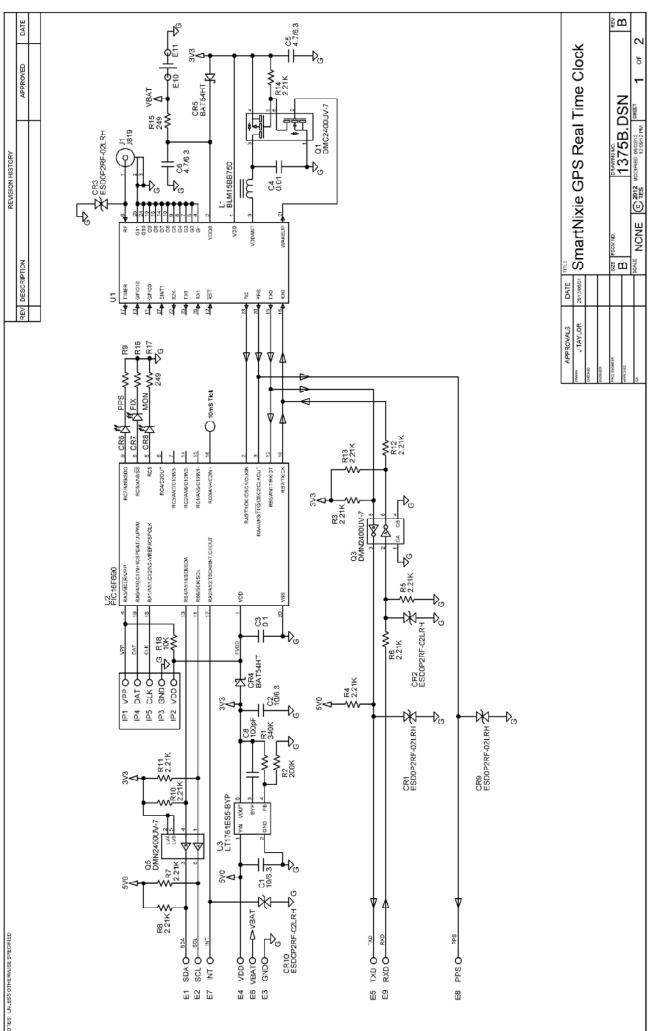

Fig 4. Typical application circuit (1375 pin numbering shown)

Taylor Electronics Services www.tayloredge.com

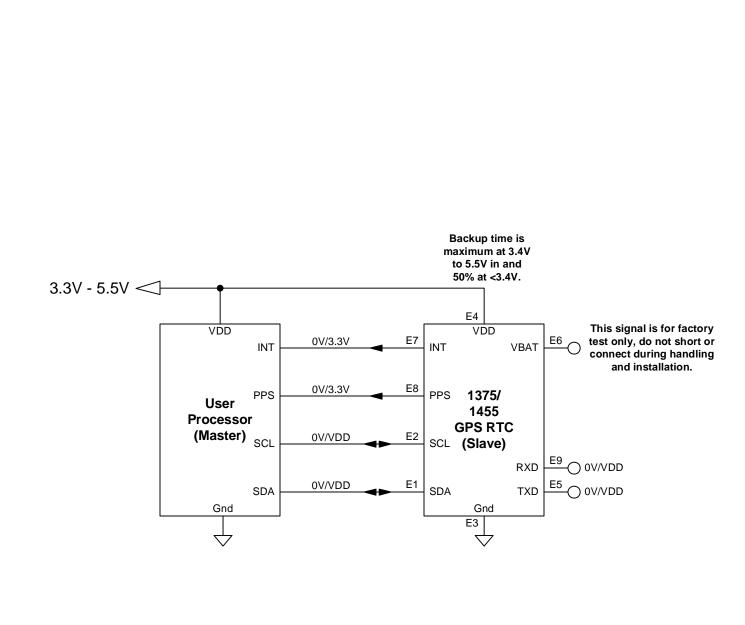

Fig 6. SmartNixie Backplane RS232 Connection

Taylor Electronics Services www.tayloredge.com

#### 6

# Taylor Electronics Services www.tayloredge.com

Setting Local Time vs UTC Offset

This functionality allows setting the local time vs UTC offset and the interrupt frequency from a clock application, duplicating the functionality or writing directly to registers 0x3B to 0x3F.

When writing to the page 0x00 time registers, if the year is set to 00 and the month is set to 01 to 12 (the setting mode) the settings are updated according to the table to the left and stored in EEPROM after the the years register is written. DL is checked for valid input of 11, 12, 21 or 22 however hr:mn:se is not checked so non-BCD/non-Time values will give unpredictable results when local time is calculated.

An I<sup>2</sup>C master communicates with the TES1375 module configured as a slave via a 128 byte register stack using standard I<sup>2</sup>C commands at a maximum data rate of 100kbps. See Table 4 for a complete list of the slave stack register functions.

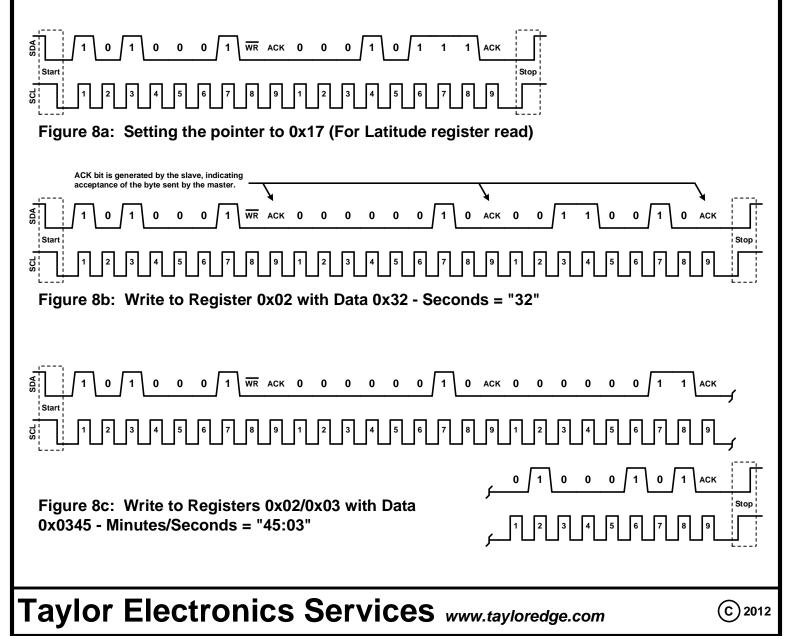

For register writes a Start command is issued followed by the slave address where the R/W bit is cleared to zero. The next byte written is the pointer to the desired element in the register stack from 0x00 to 0x7F. The following bytes written are the register data and after the last register data byte has been sent, a Stop command is issued which completes the transaction. Each write by the master is followed by a low ACK bit generated by the slave indicating an acknowledgement of the transaction, where a high NAK bit generally indicates no slave at the specified address is present. A single write consisting of the pointer byte alone sets the pointer for the next read transaction.

After each write the internal pointer is incremented allowing from 0 to 128 consecutive registers to be written in the same transaction. Writes beyond the last writeable register position (0x7F) are ignored. Read only registers (The majority of registers in this device) are not affected by being written to, while other registers such as the PCF time group are acted on indirectly.

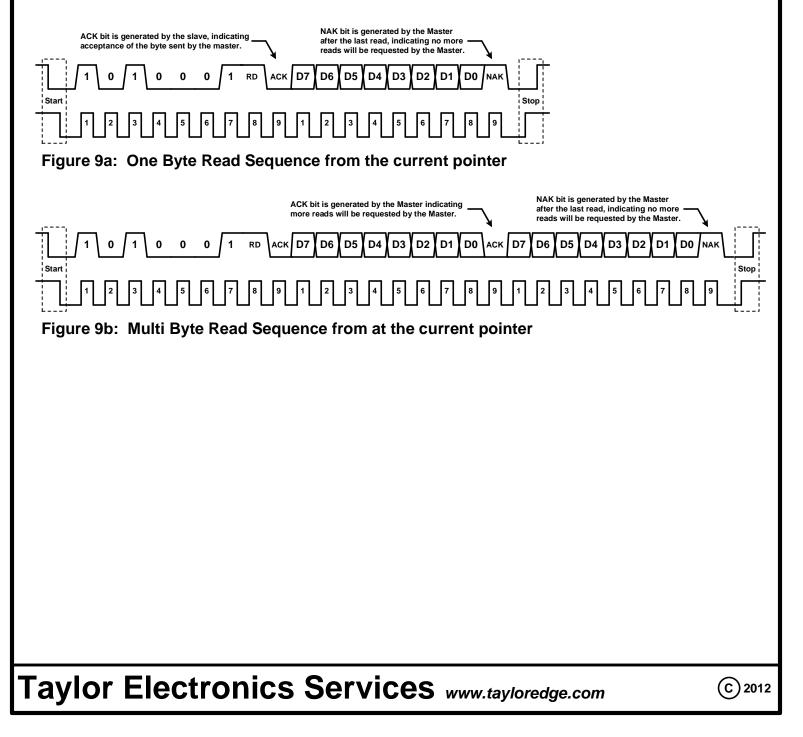

For register reads a Start command is issued followed by the slave address where the R/W bit is set to one. The first byte read is at the current pointer address. This address can be set by a single write, the pointer resulting from the last series of writes, i.e. the last byte written plus one, or the pointer resulting from the last series of reads, i.e. the last byte read plus one. Reads past the top of the register stack at 0x7F return zeros. After each read except the last, the master issues an ACK indicating the data was received. After the last read of a transaction, the master issues a NAK indicating that the data was received and no more data will be read. Following the NAK, the master issues a Stop command to terminate the transaction.

The master may perform a pointer write followed by a Stop command and then a Start command for the read sequence, or a repeated start may be used between the write and read sequences.

//Figure 8a I2C\_START(); I2C\_WRITE(0xA2); //slave address, R/W set low I2C\_WRITE(0x17); //set pointer to latitude start I2C\_STOP(); //Figure 8b I2C\_START(); I2C\_WRITE(0xA2); //slave address, R/W set low I2C\_WRITE(0x02); //set pointer to seconds register I2C\_WRITE(0x32); //write "32" to seconds register I2C\_STOP(); //Figure 8c I2C\_START(); I2C\_WRITE(0xA2); //slave address, R/W set low I2C\_WRITE(0x02); //set pointer to seconds register //write "03" to seconds register I2C\_WRITE(0x03); //write "45" to minutes register I2C\_WRITE(0x45); I2C\_STOP(); //Figure 9a I2C\_START(); //slave address, R/W set low I2C\_WRITE(0xA2); I2C\_WRITE(0x17); //set pointer to latitude start I2C\_START(); //repeat start I2C\_WRITE(0xA3);

data1=I2C\_READ(1); //slave address, R/W set high //read register 0x17 I2C\_STOP(); //last read is always (1)=NAK //Figure 9b I2C\_START(); //slave address, R/W set low I2C\_WRITE(0xA2); I2C\_WRITE(0x17); //set pointer to latitude start I2C\_START(); //top I2C\_WRITE(0xA3); //slave address, R/W I T2C\_PEAD(0); //read\_register\_0x17 //slave address, R/W set high data2=I2C\_READ(1); //read register 0x18 I2C\_STOP(); //last read is always (1)=NAK //Alternate code for Figure 9b I2C\_START(); I2C\_WRITE(0xA2); //slave address, R/W set low //set pointer to latitude start I2C\_WRITE(0x17); I2C\_STOP(); I2C\_START(); //slave address, R/W set high I2C\_WRITE(0xA3); \_\_\_\_\_\_(VAR3); data1=I2C\_READ(0); //read register 0x17 data2=I2C\_READ(1); //read register 0x18 I2C\_STOP();

Figure 10: Example coding (CCS PICC)

Taylor Electronics Services www.tayloredge.com

11

Taylor Electronics Services www.tayloredge.com